# INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH TECHNOLOGY

### **Comparison between Serial Adder and Parallel Adder**

Ashivani Dubey<sup>\*1</sup>, Jagdish Nagar<sup>2</sup>

\*1,2 Acropolis Institute of Technology and Research, Indore, India

ashvinidubey@yahoo.com

#### Abstract

In digital circuit addition process is biggest and very important process. With the help of this method digital equipment perform various types of operation such as addition multiplication etc. on the basis of working principle there are two types of adder (1) Serial adder (2) Parallel Adder. Parallel adder is faster rather then serial adder, generally this require more components but in this type of method all bits are added simultaneously.

Keywords: Serial Adder, Parallel Adder.

#### Introduction

Basically in digital system there are two type of circuit (1) Combinational logic circuit (2) Sequential logic circuit. When we talk about combinational circuit, this circuit is that circuit of which output depends on input like half adder, Full adder and in the sequentional circuit output is depend on present state like flip flop etc.

In this paper we will read a part of combinational circuit which is parallel and serial adder. Parallel adder is better then serial adder, input bit rate, working speed, quantity of input signal, in put line is large as compare to serial adder. There is one drawback of parallel adder that is need of quantity of large component.

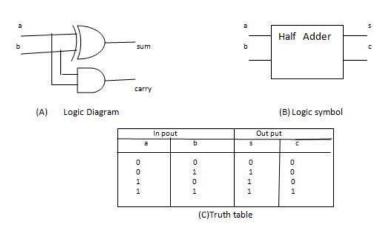

#### Half Adder

When we want to add two binary number we ware use Half adder. Half adder is very simple adder which out put is depend on its out put, that means in this adder there are two input lines (a and b)and two out put line (s and c) S is the sum and C is the carry out put point. In this type of adder there are require one EX-OR Gate and one AND Gate, EX-OR give Sum and AND Gate give Carry bit. There are Logic diagram, logic symbol and truth table are present here

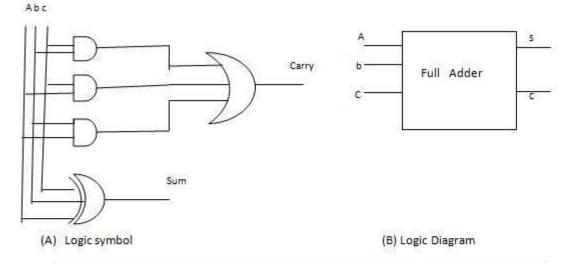

#### **Full Adder**

A half adder add only two input bits , when we want add more bit then we ware use full adder . Full adder bigger rather then half adder in this type of adder one EX-OR three AND and one OR gate is use. The EX-OR give us SUM and OR gate give us Carry output. Logic diagram is shown in figure when two or more input is high then AND gates is operated and produce Carry.

| Inputs |   |   | Outputs |   |

|--------|---|---|---------|---|

| A      | b | с | s       | с |

| 0      | 0 | 0 | 0       | 0 |

| 0      | 0 | 1 | 1       | 0 |

| 0      | 1 | 0 | 1       | 0 |

| 0      | 1 | 1 | 0       | 1 |

| 1      | 0 | 0 | 1       | 0 |

| 1      | 0 | 1 | 0       | 1 |

| 1      | 1 | 0 | 0       | 1 |

| 1      | 1 | 1 | 1       | 2 |

#### (c)Truth Table

Carry

## **Parallel Adder**

In most logic circuit addition of more than 1bit is carried out . for Example computer use 8 to 64 bit . The addition of multi bit can be accomplished using several adder. The 4 bit adder using full adder this is capable of adding two 4 bit number resulting in a 4 bit sum and a carry out put. since all bit of the augends and addend are fed in to the adder circuit simultaneously and the addition in each position are taking place at the same time , this circuit is known as Parallel adder.

Represented by A3 A2 A1 A0 =1111 and B3 B2 B1 B0 =0011.

| Place<br>Carry | $\begin{array}{c}4&3&2&1\\1&1&1&0\end{array}$ |

|----------------|-----------------------------------------------|

| Augends word A | 1 1 1 1                                       |

| Addend word B  | 0011                                          |

|                |                                               |

B3 A2 B2 A1 B1 A3 C2 C1 Сз C2 C1 Co C4 Сз Cout \$3 2S **S1 S**0 4bit binary parallel adder Through the parallel binary adder is said to

$1 \ 0 \ 0 \ 1 \ 0$

Sum

Through the parallel binary adder is said to generate its output very fast when input is applied its speed operation is limited by the carry propagation delay through all stage. In each full adder the carry input has to be generated from the previous full adder which has an inherent propogation delay. The propogation delay of full adder is the time different between the instant at which the input are applied and the instant at which is output

http://www.ijesrt.com

(C) International Journal of Engineering Sciences & Research Technology

[2570-2572]

are generated . in binary adder the output in LSB stage is generated only after tp second ,the output in second stage will be generated only after tp second from the time the output of the first stage are generated after 2tp second from the time the input are applied , the third stage will generate output 3tp second and the fourth stage will generated only after 4ts . Thus the 4 bit binary parallel adder propogation delay 50ns the out put n the forth stage will be generated only after 4tp =4x50 ns=200ns. The magnitude o such a delay is prohibitive for high speed computer. There are several method to reduce delay.

One method for speed up for this process is look- ahead carry addition, which eliminate the ripplecarry delay. The is method is based on carry generation and carry propogation function. This method requires extra circuitry for getting high speed adder. Power requirement is high as compare to serial adder because its use large circuit as compare to serial adder. Some example of parallel adder is IC 7483, BCD adder ,parallel adder phenomena is also use in parallel multiplier, binary divider.

#### **Serial Adder**

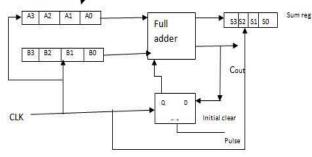

Parallel adder perform the adding two bit operation very fast but the disadvantage of this adder is its require large number of gate. One the other hand in serial adder the bit addition is bit-by-bit. Serial adder require simple circuitry as compare to parallel adder , so causes of simple circuitry this give low speed and perform bit-by-bit operation.

In this diagram there are one D flip-flop one full adder and three register are given which operated by the clock pulse . single full adder is use to add one pair of bits at a time along with carry . The D flip flop is carry flip-flop is used the carry. The contain of shift register shift from left to right and their output starting from A0 and B0 are fed in to a single full adder along with output of carry flip flop up on output application of each clock pulse.

(C) International Journal of Engineering Sciences & Research Technology [2570-2572]

#### Conclusion

Simple approach is proposed in this paper serial adder is require less number of gate for operation so power consumption is less, and serial adder is add bitby-bit so working process of serial is slow as compare to parallel adder. When we talk about parallel adder its require large number of gate so it consume large power for his circuit. Parallel adder add all bit in one of the time this give fast response. both adder are operated in CLK pulse but difference is Serial adder is add bit one by one and parallel is add all bit at a CLK pulse. There are difference table are given which indicate different between serial adder and parallel adder.

| CI | etween serial adder and paranet adder. |                            |  |  |  |

|----|----------------------------------------|----------------------------|--|--|--|

|    | Serial                                 | Parallel                   |  |  |  |

|    | adder                                  | adder                      |  |  |  |

|    | Serial adder is less                   | Parallel adder is fast as  |  |  |  |

|    | fast.                                  | compare to serial adder.   |  |  |  |

|    |                                        | It require large           |  |  |  |

|    | It require less                        | component for              |  |  |  |

|    | component for                          | operation.                 |  |  |  |

|    | operation.                             | _                          |  |  |  |

|    | •                                      | Addition process is        |  |  |  |

|    | Addition process is                    | perform by parallel        |  |  |  |

|    | perform by bit-by-bit                  | order. Means all bits add  |  |  |  |

|    | process.                               | simultaneously.            |  |  |  |

|    | -                                      | -                          |  |  |  |

|    | IT requires one full                   | No. of full adder circuit  |  |  |  |

|    | adder circuit.                         | is equal to no. of bits in |  |  |  |

|    |                                        | binary adder.              |  |  |  |

|    | Time required for                      | Time required does not     |  |  |  |

|    | addition depends on                    | depend on the number       |  |  |  |

|    | number of bits.                        | of bits'.                  |  |  |  |

|    |                                        |                            |  |  |  |

|    |                                        |                            |  |  |  |

#### Reference

S Salivahanan and S Arivazhagan, Digital circuit and design Third Edition ,Vikas Publication house pvt. ltd..

O.J.Bedrij, "Carry select adder, ire trans. Electron. Comput., pp. 340-344,1962

[3]. B. Rajkumar, H.M. Kittur "ASCI implementation of modified faster carry select adder", Eur.j.sci.res.vol.42,no.1,pp.53-58,2010